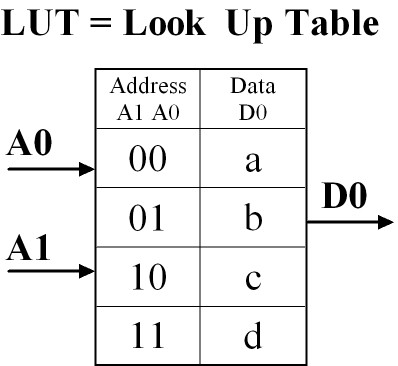

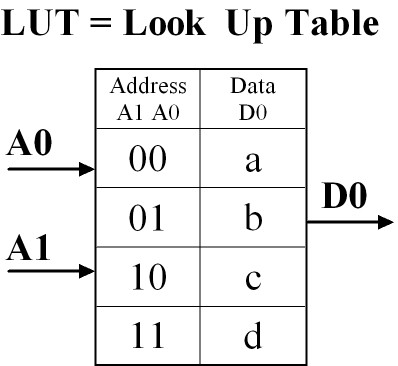

2输入1输出组合逻辑查找表

FPGA 基本功能结构 数字电路通常由组合逻辑电路和时序逻辑电路两部分构成, 对于给定输入和输出数据位宽的组合逻辑电路而言, 其可编程能力体现为 “真值表内容可由用户来动态设定”, 为了能够动态改变组合逻辑的真值表内容, FPGA 厂商 Altera 和 Xilinx 都采用了SRAM(静态RAM)的技术。如下图所示,一个2比特输入、1比特输出的 组合逻辑的真值表被存放在一个称为 查找表 Look-Up-Table 的静态RAM中, 2比特的输入信号作为RAM的 地址输入信号, RAM的数据内容为1比特, 作为组合逻辑的输出信号。

2输入1输出组合逻辑查找表 |

所谓静态RAM的含义是,RAM在上电期间 其中的内容不会丢失, 不需要进行动态刷新, 系统掉电之后,SRAM中的数据会消失,因此基于SRAM结构 的FPGA通常需要搭配固化存储器,FPGA启动时, 将固化存储器的内容搬移到SRAM中,从而实现应用逻辑功能。

对于可编程数字电路而言, 除了需要可编程的组合逻辑真值表之外, 还需要有可编程的互联结构, 因为复杂的数字电路通常存在大量的互相连接的电路逻辑单元, 因此可编程逻辑器件需要向用户提供可以进行动态互联的电路。

下图是一个Altera 公司 Cyclone III系列 FPGA 中, 可编程逻辑单元(LE, Logic Element)的电路结构图(图片来源:Altera)。 从图中可以看到, 该逻辑单元拥有一个 4输入的 LUT 作为其可编程组合逻辑电路的核心, 另外还有1比特的 D触发器用作时序逻辑单元。

可编程逻辑单元(LE, Logic Element)结构 |

除了 LUT和 D触发器之外, 从LE 的结构图中可以看到, LE中还存在大量的选择器电路用做线路的信号选通。 这些信号选通电路正是FPGA的布线可编程能力的体现,例如,以下信号选通行为,可由FPGA的用户通过编程来实现, 包括:

FPGA 的布线结构是一个层次化的布线网络, 如下图所示(图片来源:Altera), 首先由若干个依次排列的LE 构成逻辑阵列块 LAB (Logic Array Block), LAB的边上是局部布线网络, 用于连接附近的LAB。 另外还有 行、列布线网络, 用于把两个相隔较远LAB的信号线互联起来。

逻辑阵列块LAB和布线网络 |

芯片管脚的可编程能力,对于可编程数字电路来说同样非常重要, 下图是 CycloneIII FPGA芯片管脚IO单元结构图(图片来源:Altera)

CycloneIII FPGA芯片管脚IO单元结构图 |

从图中可以看到, 该芯片管脚IO单元的可编程能力主要体现为如下几点:

下图是一颗成熟FPGA芯片 的 内部结构图(图片来源:Altera Quartus Chip Planner) 图中展示了FPGA芯片中, 各种功能组件的分布, 除了 LE、 LAB、 布线通道、 IOE 这些 FPGA的基本组件之外, 图中芯片还有 诸如 锁相环(PLL) , 内存块( RAM block) 这些 增强型的组件。 限于篇幅, 此处不讨论增强型组件。

Cyclone FPGA 功能组件分布 |

如前文所述, SRAM 结构的 FPGA 器件 掉电后编程信息会消失, 因此 FPGA芯片外部需要有一颗固化编程代码的启动配置芯片, 系统上电后 FPGA从该启动配置芯片读取编程信息配置自身内部的可编程电路。 下图是 Altera FPGA芯片使用AS模式(Active Serial) 和EPCS系列型号串行启动芯片的电路连接方式 (图片来源:Altera), 从图中可以看到, FPGA芯片通过 DCLK/nCS/ASDO 管脚向 EPCS系列芯片(Serial Configuration Device)发送指令时序信号, EPCS芯片通过 DATA 管脚向FPGA 输出 电路编程配置数据。

CycloneIII FPGA芯片 AS启动 电路图 |

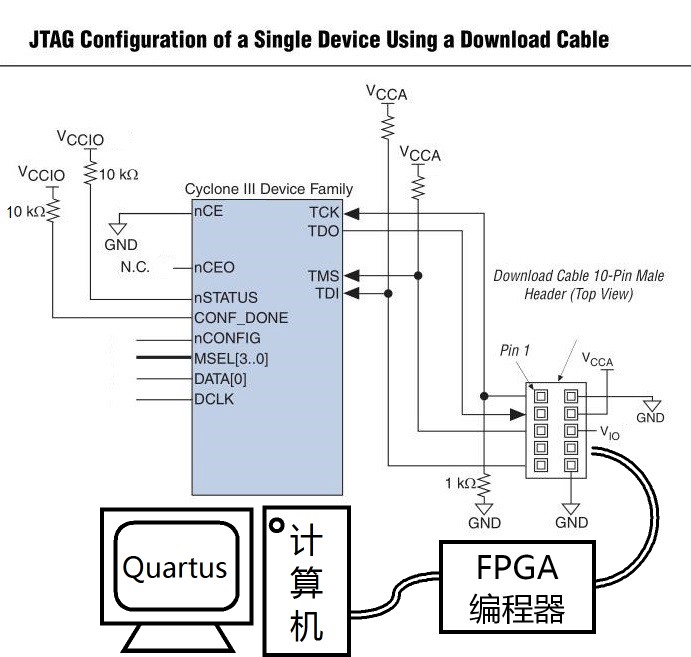

由于 FPGA 的 启动配置芯片通常采用Flash工艺结构, 因此每次写入芯片时 需要进行 区块数据擦除、 坏块检查、 写入数据校验等 操作, 并且由于 Flash 存储器的写入速度较慢, 从而导致使用计算机和FPGA编程器将编程数据向固化存储器的写入过程时间较长(通常为若干分钟) 。

由于固化数据的写入速度较慢, 在进行开发调试时需要快速验证系统功能, 通常会采用另外的下载模式, 比如使用编程器连接 FPGA的JTAG接口, 将计算机上的FPGA编程数据文件直接写入到FPGA芯片内部, 这种直接下载到FPGA内部的编程数据掉电后会丢失, 但是由于其下载速度 较快, 比较利于电路开发调试时快速进行设计迭代。 下图是 JTAG模式的 FPGA电路连接图 。(图片来源:Altera)

从图中可以看到, JTAG接口使用TCK管脚向FPGA发送时钟、 TMS(测试模式选择)管脚 向FPGA 发送配置模式信息 、TDI 管脚 向 FPGA写入数据, 以及使用TDO管脚从FPGA读取数据。 由于不需要进行额外的擦除、校验等工作流程, JTAG的下载写入速度通常较快(通常为若干秒)。

CycloneIII FPGA芯片 JTAG 接口 电路图 |