逻辑门与真值表

(图片来源:learn.sparkfun.com/tutorials/digital-logic )

FPGA电路逻辑的原理图方式设计与验证对于先修过本科数字电路课程,但是尚未接触过FPGA的EDA设计流程的同学而言, 在FPGA的设计工具中, 使用原理图的方式, 把本科数字电路中熟悉的74系列集成电路, 在EDA工具中重新应用一次, 不失为一种好的入门方法。 本实验使用两种常用的74系列集成电路, 分别是 74138 译码器,以及74161 计数器 作为入门的实验芯片。

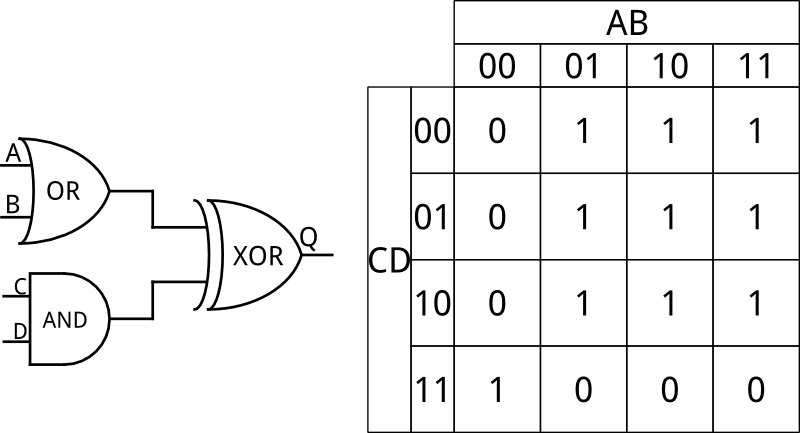

我们最早从本科数字设计的课程中接触数字逻辑设计时,对于组合逻辑, 首先定义出输入和输出的接口,然后绘制出输入数据和输出结果之间的真值表。 接下来根据真值表绘制卡诺图。 最后根据真值表以及所绘制的卡诺图, 用逻辑门拼接出真值表所的一种实现形式,例如下图是一个真值表及其对应的一种逻辑门实现方式。

逻辑门与真值表 (图片来源:learn.sparkfun.com/tutorials/digital-logic ) |

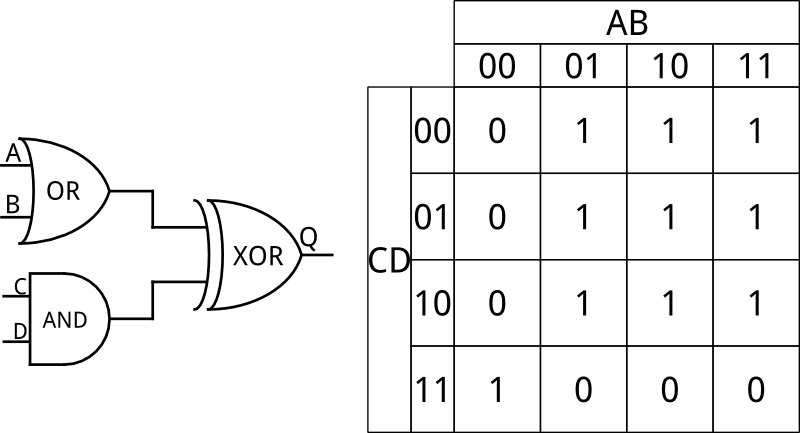

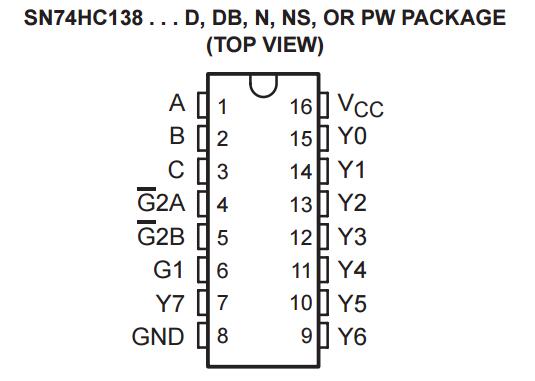

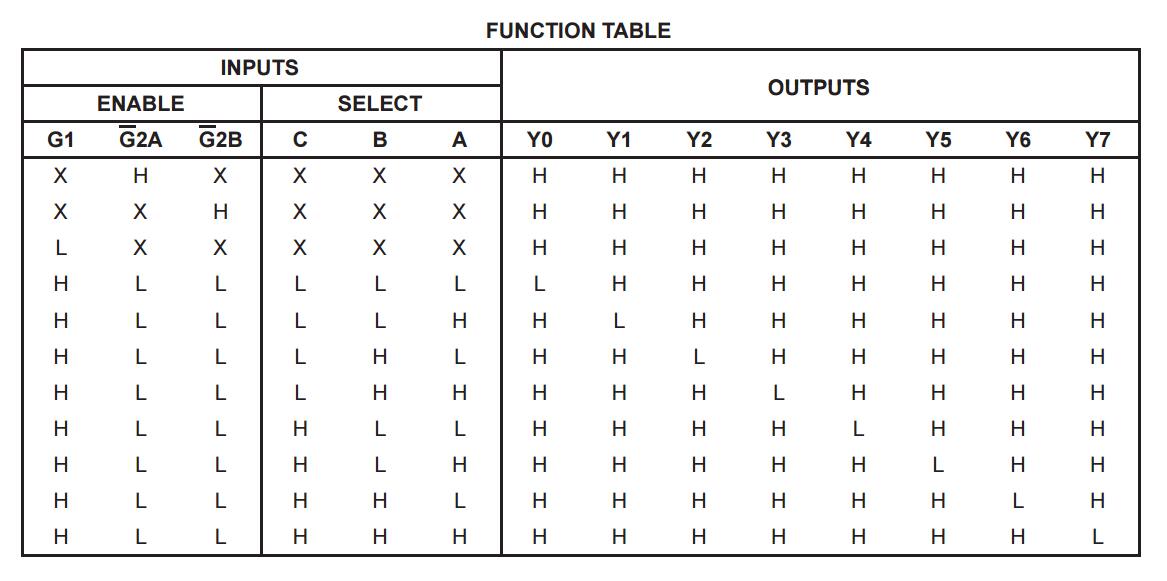

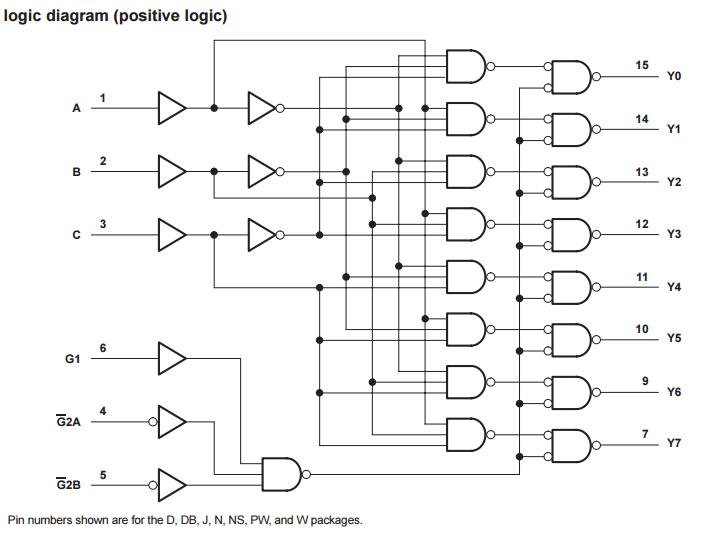

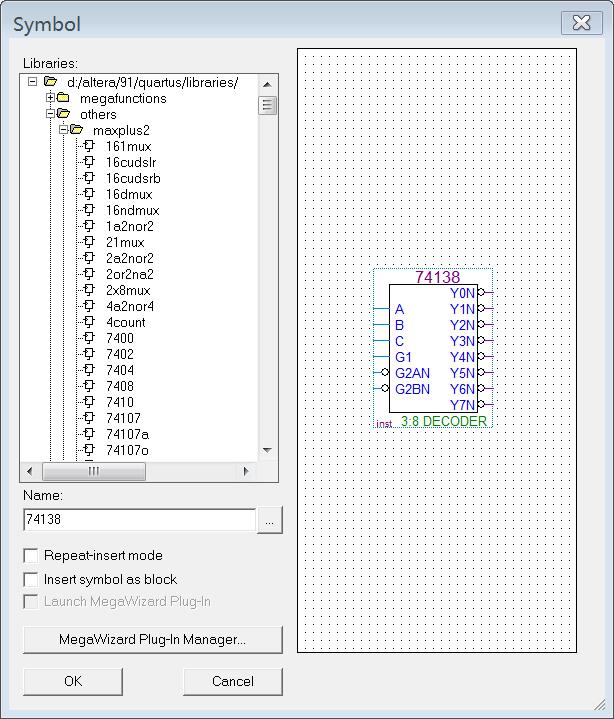

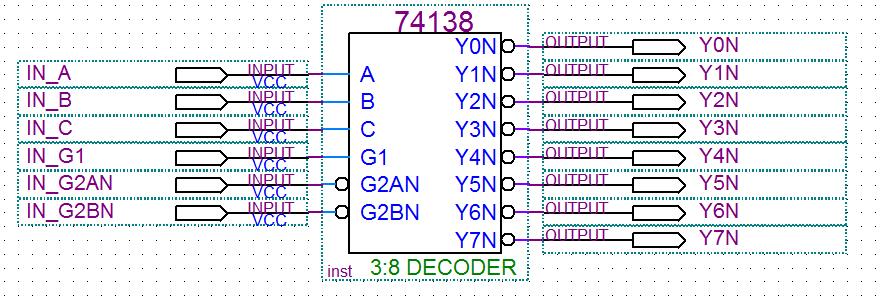

在数字集成电路的早期时代, 对于一些常用的小型逻辑, 比如3-8 译码器 会被集成进一颗芯片, 例如74138芯片就是一颗实现3-8译码器的常用组合逻辑芯片。 下图分别是74138芯片的管脚定义、真值表以及内部逻辑结构

74138芯片管脚定义 (图片来源:德州仪器 ) |

74138芯片真值表 (图片来源:德州仪器 ) |

74138芯片内部逻辑结构 (图片来源:德州仪器 ) |

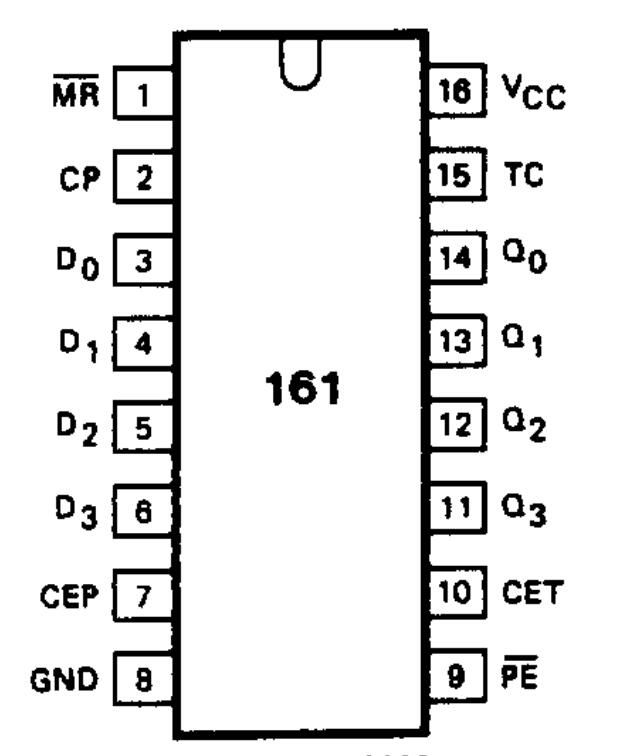

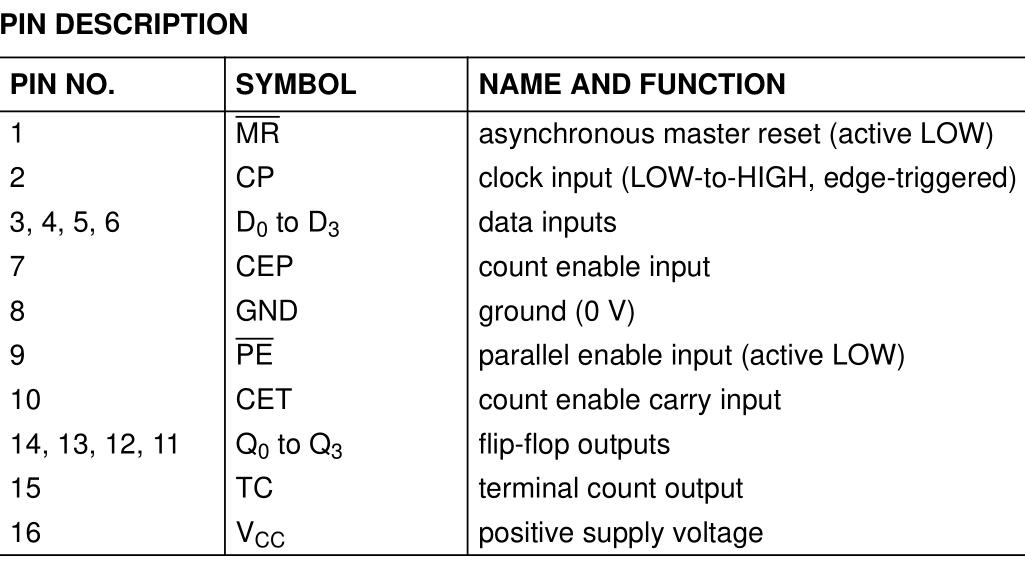

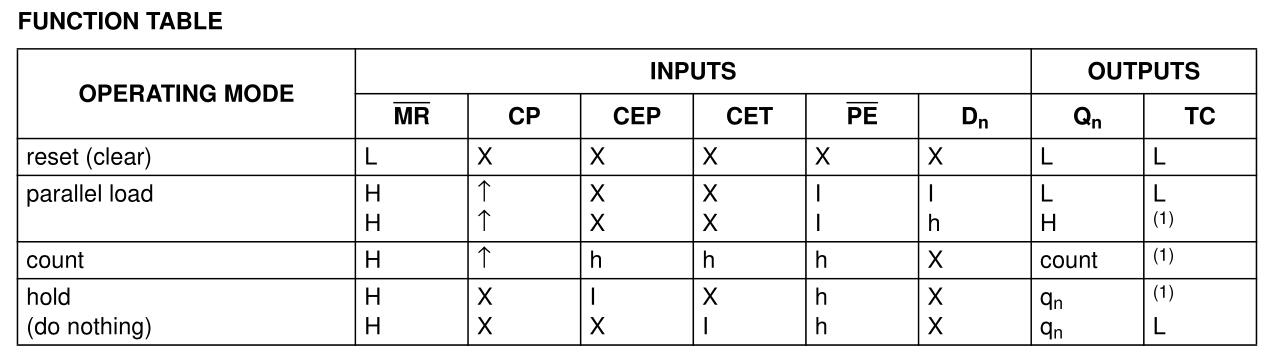

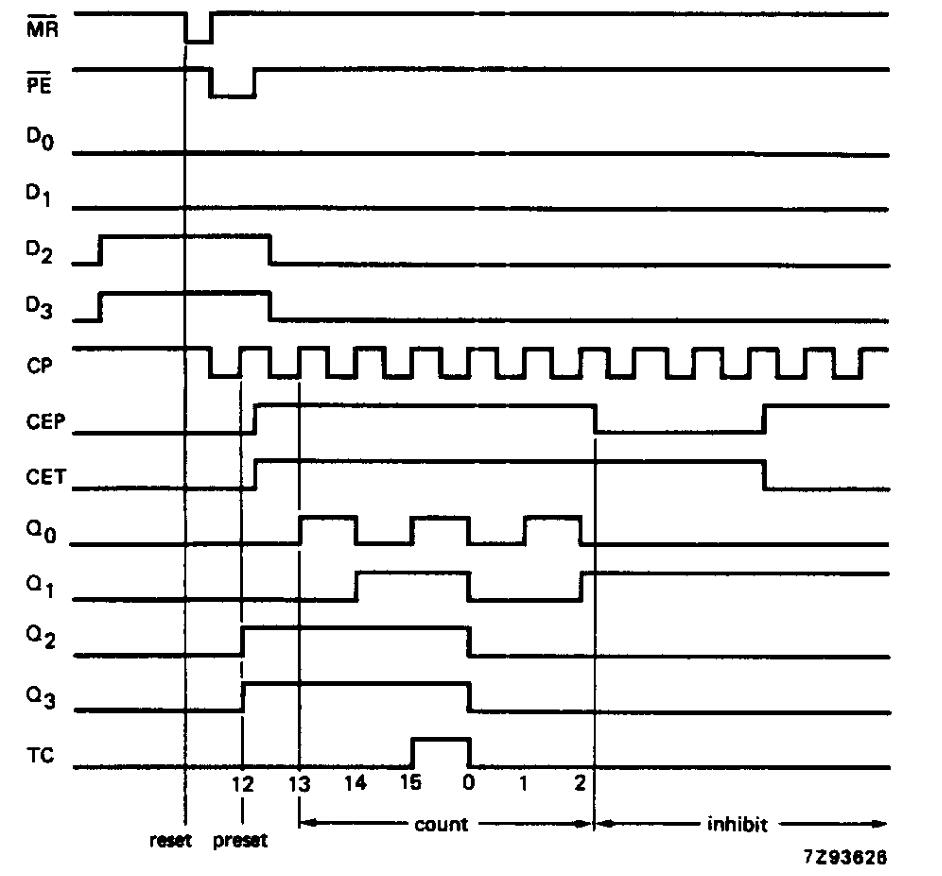

同样,对于一些常用的时序逻辑电路, 比如4比特的计数器,也会被设计成一颗芯片, 用于给更复杂的系统作为零件。 例如, 74161就是一颗用来实现带置位功能的4比特16进制计数芯片。下图是74161芯片的相关信息。

74161芯片引脚序号 (图片来源:德州仪器 ) |

74161芯片引脚功能 (图片来源:德州仪器 ) |

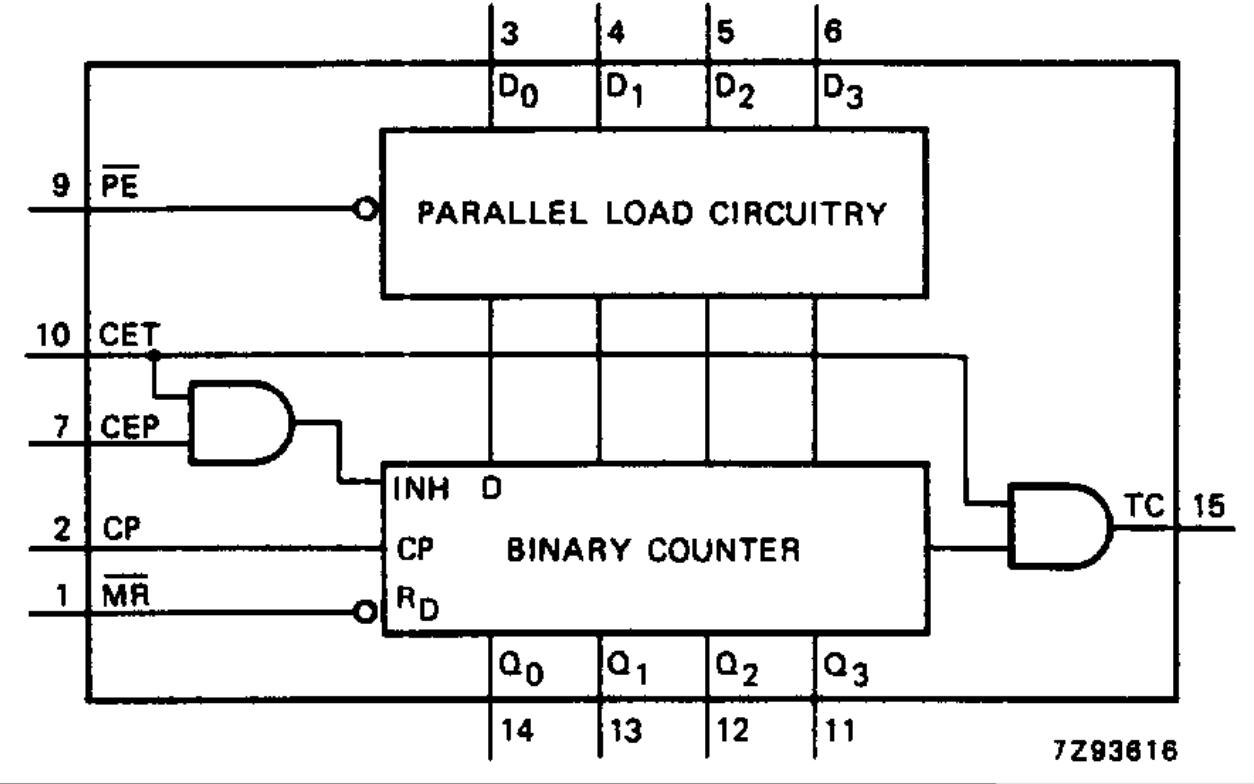

下图是74161芯片的内部结构图,从图中可以看到,161芯片内部主要包括一个4比特计数器和一个并行置数电路, 另外还有2个逻辑门用于工作使能和进位控制。

74161芯片内部结构 (图片来源:德州仪器 ) |

74161芯片的工作逻辑真值表和工作时序如下图所示

74161逻辑真值表 (图片来源:德州仪器 ) |

74161时序图 (图片来源:德州仪器 ) |

74138添加组件符号 |

在BDF中放置138,设定输入输出管脚 |

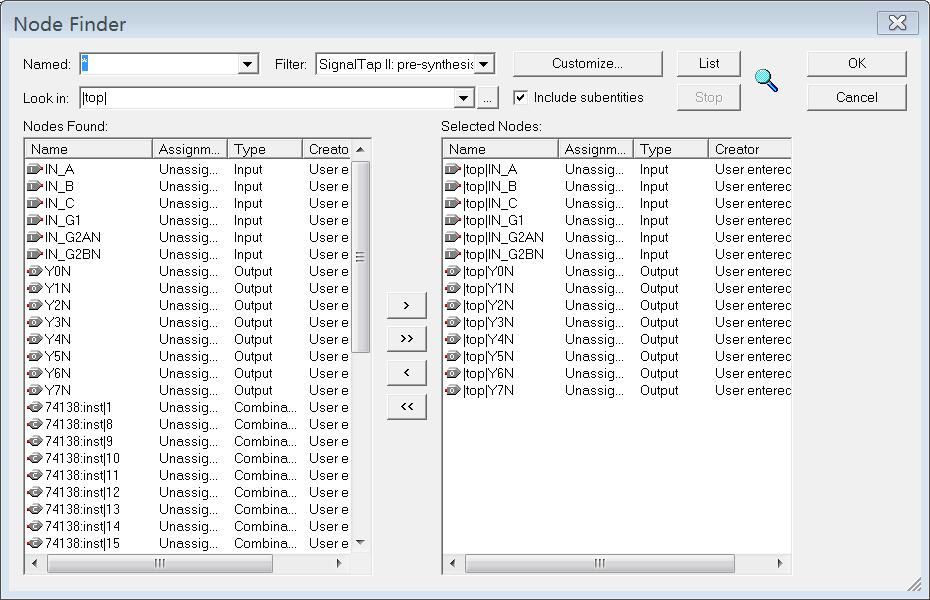

在VWF文件中,使用NodeFinder 添加 仿真信号 |

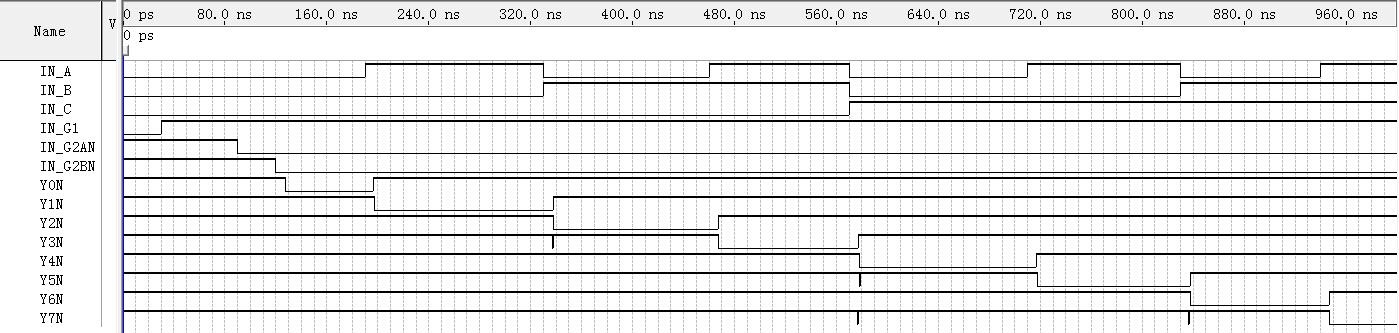

运行仿真,观察结果波形 |

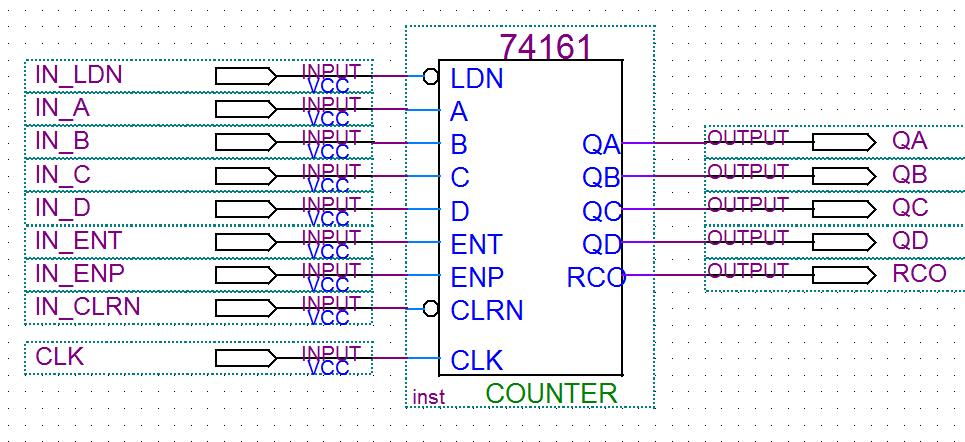

在BDF中放置161,设定输入输出管脚 |

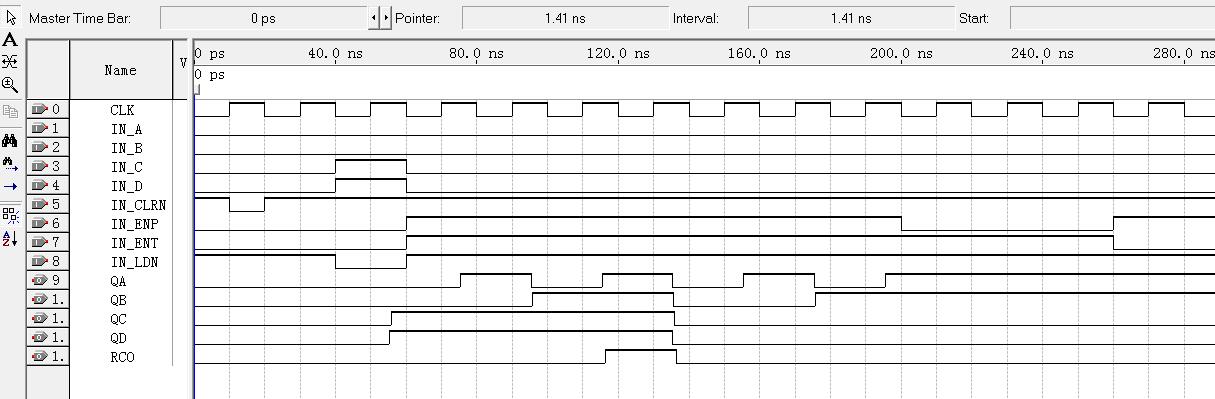

运行仿真,观察计数器的结果波形 |

从以上我们执行的FPGA设计过程,是FPGA电路设计流程中,最容易上手的设计、验证方式。该流程有以下特征:

通过以上实验,可以看到,使用FPGA芯片,可以把小规模数字逻辑时代的各种数字电路移植到FPGA芯片中, 并且这种设计方式, 相对制作电路实物再调试的方式, 更加有效率。

然而, 这种在图形上连接74芯片的设计方式, 除了移植一个旧设计之外, 并不是一种很高效率的设计方法。 因为把一个复杂逻辑设计, 映射为74芯片或是门电路的过程, 需要很多的人工设计, 比较繁琐。

正因为如此, 数字电路EDA行业, 发展出基于HDL(硬件描述语言)的设计和验证流程, 这种流程可以使用代码文本来描述 电路的功能与结构, 之所以集成电路会选择这种设计方式, 是因为计算机工具最擅长处理的信息表达方式, 是文本和代码, 并且, 最易于计算机重复使用的信息格式,也是文本和代码。 后续教程中我们会使用 verilog HDL 代码来描述电路, 相比于原理图而言,这是一种更加有效率的设计方式。